Во время проведения мероприятия IEEE International Electron Device Meeting (IEDM) в Сан-Франциско производители чипов рассказывали о том, какие технологические решения они вскоре начнут использовать для выпуска своей продукции.

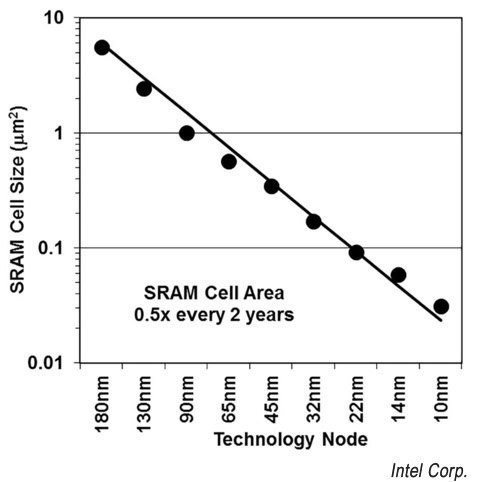

Исследователи Intel представили 10-нанометровую технологическую платформу и заявили, что она обеспечивает превосходную производительность транзисторов и межсоединений, а также отличную масштабируемость проектирования. Также были продемонстрированы возможности платформы в виде чипа SRAM объёмом 204 МБ, который включает три различных типа ячеек памяти: ячейки высокой плотности площадью 0,0312 мкм2, ячейки с низким энергопотреблением площадью 0,0367 мкм2, высокопроизводительные ячейки площадью 0,0441 мкм2.

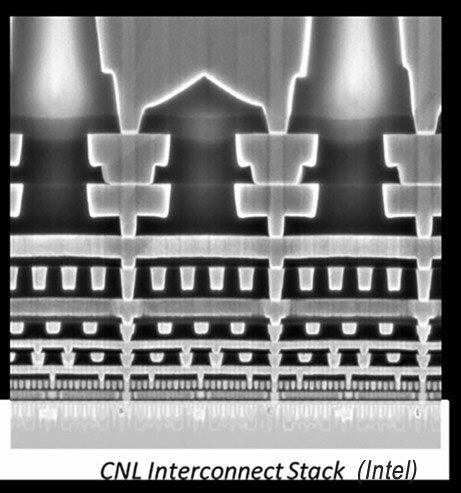

Платформа предусматривает использование производственной технологии FinFET третьего поколения с применением SAQP для критических слоёв (self-aligned quadruple patterning), что обеспечивает ширину пластины в 7 нм при шаге 34 нм и высоту пластины 46 нм; технологии High-k пятого поколения; технологии растянутого кремния седьмого поколения. Также отмечается, что Intel использует кобальт в двух нижних слоях межсоединений в рамках 10-нанометрового техпроцесса. Благодаря внедрению кобальта удалось в 5-10 раз улучшить ситуацию электромиграцией и в 2 раза уменьшить сопротивление. Все указанные новшества позволили повысить ток NMOS и PMOS на 71% и 35%, соответственно, по сравнению с 14-нанометровой производственной технологией FinFET.

Компания GlobalFoudries заявила, что в рамках 7-нанометровой производственной технологии она продолжит использовать комбинацию меди и High-k диэлектриков, как и в предыдущих технологиях. Это обеспечит ряд преимуществ, таких как высокая надёжность, меньшая сложность и более высокие нормы выхода годной продукции. Также исследователи компании представили полностью интегрированную 7-нанометровую CMOS платформу, которая обеспечивает значительную масштабируемость плотности компонентов и повышение производительности по сравнению с 14-нанометровой производственной технологией. В рамках этой платформы применяются технология FinFET третьего поколения с SAQP (self-aligned quadruple patterning) для формирования пластин и SADP (self-aligned double patterning for metallization) для металлизации.

Вместе с тем, компания рассказала, что технологическая платформа была разработана с возможностью использования преимуществ EUV-литографии для определённых уровней с несколькими шаблонами. Это позволит повысить эффективность производства. При этом в GlobalFoudries заявляют, что некоторые параметры EUV-литографии всё ещё нуждаются в доработке. Тем не менее, компания уже начала устанавливать соответствующее производственное оборудование для EUV-литографии на своей фабрике Fab 8 в штате Нбю-Йорк.

GlobalFoudries отмечает, что 7-нанометровая производственная платформа обеспечивает 2,8-кратное преимущество в плотности разводки по сравнению с 14-нанометровой производственной технологией. Также заявлен прирост производительности при неизменном энергопотреблении более чем на 40% или же снижение энергопотребления на 55% при неизменной частоте.

GlobalFoudries предлагает полный набор необходимого базиса и интеллектуальной собственности в рамках своей улучшенной производственной CMOS платформы. Она позволит создавать высокопроизводительные компьютерные и мобильные решения.

Хотя на презентациях Intel и GlobalFoudries не было представлено подробных технических деталей, улучшения в плотности размещения транзисторов по сравнению с предыдущим поколением идёт почти в ногу с законом Мура.

-

-